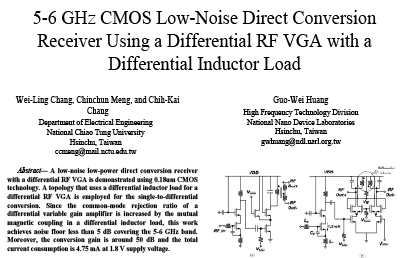

Fig. 4 shows the die photo of a 5-6 GHz low-noise lowpower I Q DRC in 0.18μm CMOS technology. and the die-size is 1.5 x 1 mm2 including the DC RF pads. By on-wafer measurement. the total current consumption is 4.75mA at the supply voltage of 1.8 V. Fig. 5 indicates the conversion gain and the input return loss with respect to RF frequency. The peak gain is 50 dB at 5.4 GHz and the 3-dB bandwidth is from 5.1 GHz to 5.9 GHz. Also. the return loss is better than 10 dB for the whole operating frequency range. By properly biasing the mixer core. the LO pumping power is about 6 dBm to achieve fully current commutation as shown in Fig. 6. Fig. 7 shows the noise performance of this work. At the measurement frequency point of 5.2 5.5 5.8 GHz. the flicker noise corner is around 1 MHZ as expected for the active MOS mixer [1] and the noise floor can be less than 6 5 5 dB. respectively.

Iran Energy News Oil, Gas, Petrochemical and Energy Field Specialized Channel

Iran Energy News Oil, Gas, Petrochemical and Energy Field Specialized Channel