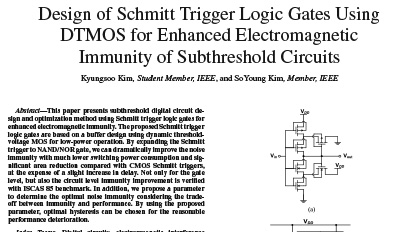

As the supply voltage of a circuit decreases. noise immunity becomes more important to guarantee signal integrity. This paper presents a method of improving noise immunity applicable to subthreshold circuits. The traditional method for immunity enhancement is to use a Schmitt trigger. which requires an additional current path to adjust the switching threshold voltage and a large area. However. by utilizing the proposed VTMOS scheme. which adjusts the threshold voltage of the MOS transistor to implement the hysteresis of the transfer characteristics. both area and switching power consumption can be significantly reduced while simultaneously providing improved noise immunity. at the expense of a slight increase in delay. Therefore. the proposed VTCMOSbased digital logic design can enable noise-immune low-power IC design.

Iran Energy News Oil, Gas, Petrochemical and Energy Field Specialized Channel

Iran Energy News Oil, Gas, Petrochemical and Energy Field Specialized Channel